# **SIEMENS**

## SIMATIC NET

# **PROFIBUS Controller** SPC 4<sup>®</sup>-2 LF

Manual

1 **Functional Overview** Pin Assignment 3 **Memory Assignment FLC Interface** 5 **DP Interface** 6 ASIC Interface 7 **Asynchronous Interface** 8 **Synchronous Interface Clock Pulses** 10 **Processor Interface** 11 **Technical Specifications 12 Package** 13

14

15

16

Contents

Introduction

References

Addresses

**Appendix**

C79000-G8976-C157-3

# 北京科迪通达科技有限公司 Beijing K.D.T.D Technology CO.,LTD

中国·北京市海淀区知春路 108 号豪景大厦 C 座 1801 室

电话: 010-62145819 62612148

传真: 010-62623015 邮箱: ic@kdtd.net

## PROFIBUS&PROFINET 授权中国代理商

## PROFIBUS 协议通讯芯片

| SPC3        | STEP C  | 96/Tray  | 960/Pack  |

|-------------|---------|----------|-----------|

| SPC3LV      | STEP C  | 160/Tray | 800/Pack  |

| VPC3+CLF3   |         | 96/Tray  | 960/Pack  |

| DPC31       | STEP C  | 66/Tray  | 660/Pack  |

| LSPM2       |         | 66/Tray  | 660/Pack  |

| SPC4-2      |         | 160/Tray | 800/Pack  |

| SIM1-2      |         |          | 1000/Reel |

| ASPC2R/STE2 | $^{2}A$ | 66/Tray  | 660/Pack  |

## PROFINET 协议通讯芯片

| ERTEC 200 | 70/Tray | 350/Pack |

|-----------|---------|----------|

| ERTEC 400 | 70/Tray | 350/Pack |

## PROFIBUS&PROFINET 开发套件

PROFIBUS-DP 开发套件 PROFIBUS-PA 开发套件 PROFINET-ERTEC200 开发套件 PROFINET-ERTEC400 开发套件

请直接联系我们或者访问我们的网站 www.kdtd.net

## **Classification of Safety-Related Notices**

This document contains notices which you should observe to ensure your own personal safety, as well as to protect the product and connected equipment. These notices are highlighted in the manual by a warning triangle and are marked as follows according to the level of danger:

#### **Danger**

indicates that death, severe personal injury **will** result if proper precautions are not taken.

### Warning

indicates that death, severe personal injury **can** result if proper precautions are not taken.

#### Caution

with a warning triangle indicates that minor personal injury can result if proper precautions are not taken.

#### Caution

without a warning triangle indicates that damage to property can result if proper precautions are not taken.

#### Notice:

indicates that an undesirable result or status can result if the relevant notice is ignored.

#### Note

highlights important information on the product, using the product, or part of the documentation that is of particular importance and that will be of benefit to the user.

Copyright © Siemens AG, 2001 bis 2006

Disclaimer

We have checked the contents of this manual for agreement with the hardware and software described. Since deviations cannot be precluded entirely, we cannot guarantee full agreement. However, the data in this manual are reviewed regularly and any necessary corrections included in subsequent editions. Suggestions for improvement are welcome.

Siemens AG Automation and Drives Industrial Communication Postfach 4848, D-90327 Nürnberg

C79000-G8976-C157-3

Technische Änderungen vorbehalten.

#### **Trademarks**

SIMATIC®, SIMATIC NET®, SINEC® and SIMATIC NET Networking for Industry® are registered trademarks of Siemens AG.

Third parties using for their own purposes any other names in this document which refer to trademarks might infringe upon the rights of the trademark owners.

### **Safety Instructions Regarding your Product**

Before you use the product described here, read the safety instructions below thoroughly.

#### **Qualified Personnel**

Only qualified personnel should be allowed to install and work on this equipment . Qualified persons are defined as persons who are authorized to commission, to ground, and to tag circuits, equipment, and systems in accordance with established safety practices and standards.

## **Correct Usage of Hardware Products**

Note the following:

#### Caution

This product may only be used for the applications described in the catalog or the technical description, and only in connection with devices or components from other manufacturers which have been approved or recommended by Siemens.

This product can only function correctly and safely if it is transported, stored, set up, and installed correctly, and operated and maintained as recommended.

Before you use the supplied sample programs or programs you have written yourself, make certain that no injury to persons nor damage to equipment can result in your plant or process.

EU Directive: Do not start up until you have established that the machine on which you intend to run this component complies with the directive 98/37/EG.

## **Correct Usage of Software Products**

Note the following:

#### Caution

This software may only be used for the applications described in the catalog or the technical description, and only in connection with software products, devices or components from other manufacturers which have been approved or recommended by Siemens.

Before you use the supplied sample programs or programs you have written yourself, make certain that no injury to persons nor damage to equipment can result in your plant or process.

## **Prior to Commissioning**

Prior to commissioning, note the following warning:

#### Caution

Prior to startup read the relevant documentation. For ordering data of the documentation, please refer to catalogs or contact your local Siemens representative.

# **Contents**

| 1 | Introd                                                             | Introduction9                                                                                                                                                    |                                      |  |  |  |

|---|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|--|

| 2 | Functi                                                             | ional Overview                                                                                                                                                   | . 11                                 |  |  |  |

| 3 | Pin As                                                             | ssignment                                                                                                                                                        | . 15                                 |  |  |  |

| 4 | Memo                                                               | ry Assignment                                                                                                                                                    | . 19                                 |  |  |  |

|   | 4.1                                                                | Addressing the SPC 4-2                                                                                                                                           | . 20                                 |  |  |  |

|   | 4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                   | Structure of the Internal RAM  Overview  RAM Parameter Block  SAP List  Data Areas in the Internal RAM  Addressing Using the Memory Window                       | . 22<br>. 22<br>. 24<br>. 24         |  |  |  |

|   | 4.3                                                                | Assignment of the Parameter Registers                                                                                                                            | . 28                                 |  |  |  |

| 5 | FLC Ir                                                             | nterface                                                                                                                                                         | . 33                                 |  |  |  |

|   | 5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7 | SAP List Structure of the SAP List Control Byte Request SA. Request SSAP Access Byte Reply-Update-Ptr/ SDN-/DDB-Tln-Tab-Ptr: Special Features of the DEFAULT SAP | . 34<br>. 37<br>. 38<br>. 38<br>. 38 |  |  |  |

|   | 5.2                                                                | SM-SAP List                                                                                                                                                      | . 43                                 |  |  |  |

|   | 5.3<br>5.3.1<br>5.3.2                                              | Indication Queue  Description  Structure of the Indication Block                                                                                                 | . 44                                 |  |  |  |

|   | 5.4<br>5.4.1<br>5.4.2                                              | Reply-on-Indication Blocks  Description  Structure of the Reply-on-Indication Blocks                                                                             | . 47                                 |  |  |  |

| 6 | DP Int                                                             | erface                                                                                                                                                           | . 51                                 |  |  |  |

|   | 6.1                                                                | Description                                                                                                                                                      | . 52                                 |  |  |  |

|   | 6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6          | Productive Services Data Exchange Read-Input-Data Read-Output-Data Global Control (Sync, Freeze, Clear Data) Leave-Master Baudrate Search                        | . 55<br>. 57<br>. 58<br>. 59<br>. 61 |  |  |  |

| 7 | ASIC I                                                             | nterface                                                                                                                                                         | . 63                                 |  |  |  |

|   | 7.1<br>7.1.1                                                       | Latch Parameters                                                                                                                                                 | . 65<br>65                           |  |  |  |

|   | 7.1.2            | Baudrate Register                                      |     |

|---|------------------|--------------------------------------------------------|-----|

|   | 7.1.3            | BEGIN-PTR Register                                     |     |

|   | 7.1.4<br>7.1.5   | UMBR-PTR RegisterBASE-PTR Register                     |     |

|   | 7.1.6            | TRDY Register                                          |     |

|   | 7.1.7            | PREAMBLE Register                                      |     |

|   | 7.1.8            | SYN-Time Register                                      |     |

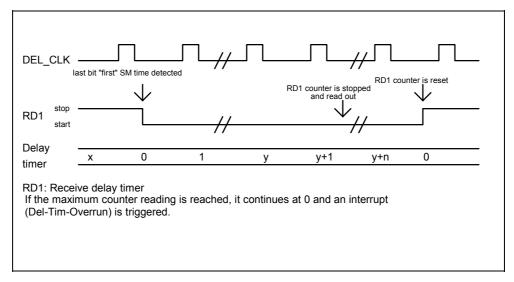

|   | 7.1.9            | Delay-Timer Register                                   |     |

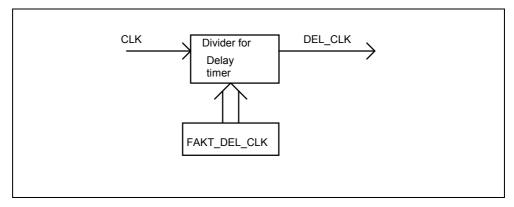

|   | 7.1.10           | Factor-Delay-Timer-Clock Register                      |     |

|   | 7.1.11<br>7.1.12 | Mode Register                                          |     |

|   | –                |                                                        |     |

|   | 7.2              | Fail-safe Mode                                         |     |

|   | 7.3              | Time-of-Day Synchronization                            | 84  |

|   | 7.4              | DDB Mechanism                                          |     |

|   | 7.5              | Activating the Extensions                              | 86  |

|   | 7.6              | Memory Expansion to 3 Kbytes                           |     |

|   | 7.6.1            | Memory Wastage with 16-Byte Segments                   |     |

|   | 7.6.2            | Mem-Overflow Interrupt with 16-Byte Segments           | 88  |

|   | 7.7              | FF Mode                                                |     |

|   | 7.7.1            | Send and Receive Buffer Structure                      |     |

|   | 7.7.2<br>7.7.3   | SendingReceiving                                       |     |

|   |                  | -                                                      |     |

|   | 7.8              | Error Trigger Signal                                   |     |

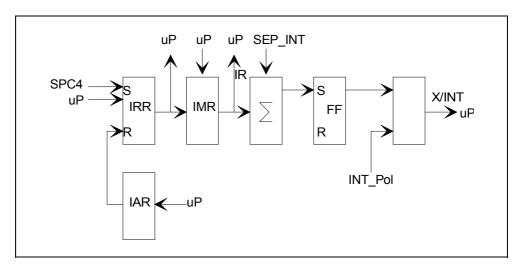

|   | 7.9              | Interrupt Controller                                   |     |

|   | 7.9.1<br>7.9.2   | Interrupt Assignment in the FF Mode                    |     |

|   | -                |                                                        |     |

|   | 7.10             | Clock Synchronization                                  |     |

|   | 7.11             | SPC 4-2-Timers                                         |     |

|   | 7.11.1           | Delay Timer                                            |     |

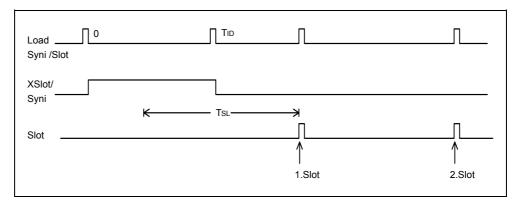

|   | 7.11.2           | Idle TimerSyni-Timer                                   |     |

|   | _                | Slot Timer                                             |     |

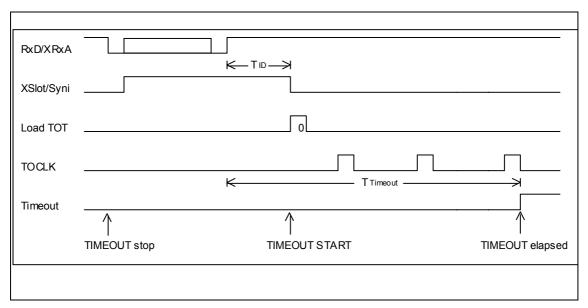

|   |                  | Timeout Timer                                          |     |

|   |                  | New Timers in the FF Mode                              |     |

| 8 | Async            | hronous Interface                                      | 107 |

|   | 8.1              | Baud Rate Generator                                    | 108 |

|   | 8.2              | Transmitter                                            | 109 |

|   | 8.3              | Transmitter                                            | 110 |

|   | 8.4              | Serial Bus Interface PROFIBUS Interface (Asynchronous) | 111 |

|   | 8.4.1            | Interface Signals                                      |     |

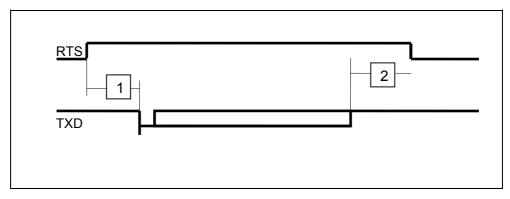

|   | 8.4.2            | RS-485 Timing                                          |     |

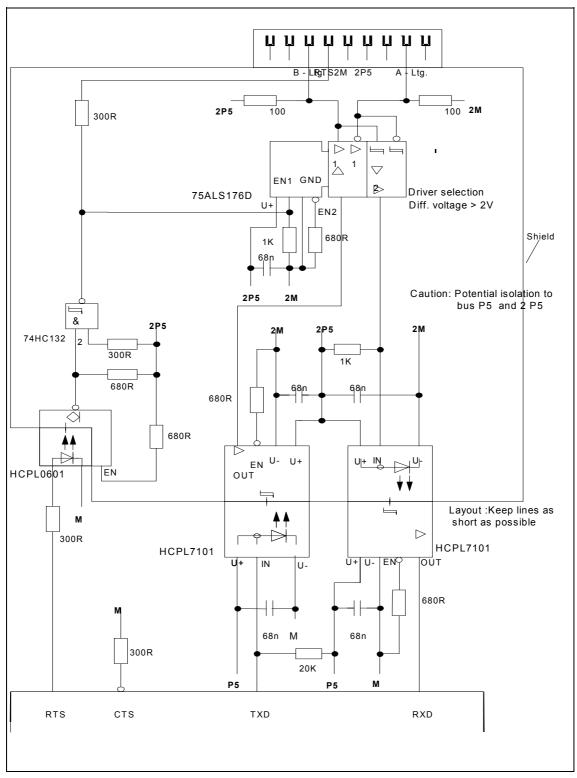

|   | 8.4.3            | Suggested Wiring for RS-485                            | 113 |

| 9 | Synch            | ronous Interface                                       | 115 |

|   | 9.1              | Overview                                               | 116 |

|   | 9.2              | Baud Rate Generator                                    | 117 |

|    | 9.3                      | Transmitter                                                                   | 118        |

|----|--------------------------|-------------------------------------------------------------------------------|------------|

|    | 9.4                      | Receiver                                                                      | 121        |

|    | 9.5                      | Pulse Modulation in the SPC 4-2                                               | 122        |

|    | 9.6                      | Pulse Demodulation                                                            | 123        |

|    | 9.7                      | Fast Synchronizer in the Manchester Receiver                                  | 124        |

| 10 | Clock                    | Pulses                                                                        | 125        |

| 11 | Proces                   | ssor Interface                                                                | 129        |

|    | 11.1                     | Universal Processor Interface                                                 | 130        |

|    | 11.2                     | Bus Interface Unit (BIU)                                                      | 133        |

|    | 11.3<br>11.3.1           | Dual-Port RAM Controller  Function  Access to the SPC 4-2 with LOCK Activated | 134        |

|    | 11.3.2                   | Other Pins                                                                    |            |

|    | 11.4.1                   | Test PinsXHOLDTOKEN                                                           | 136        |

|    | 11.5                     | Interrupt Timing                                                              | 137        |

|    | 11.6                     | Reset Timing                                                                  | 138        |

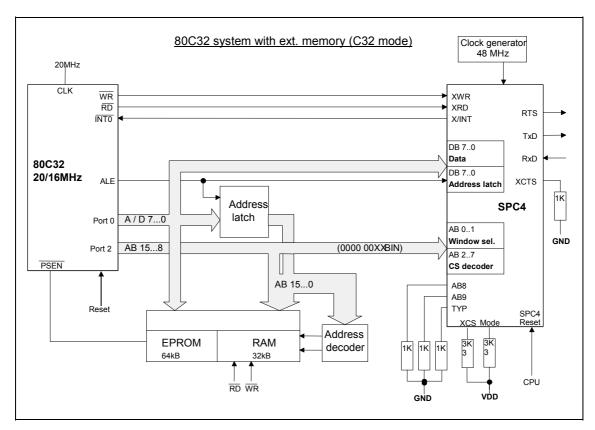

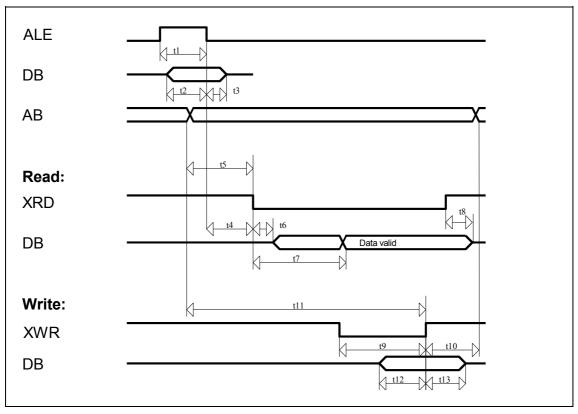

|    | 11.7<br>11.7.1<br>11.7.2 | Intel /Siemens 8051 (synchronous) etc. Circuit Diagram Timing 80C32           | 139        |

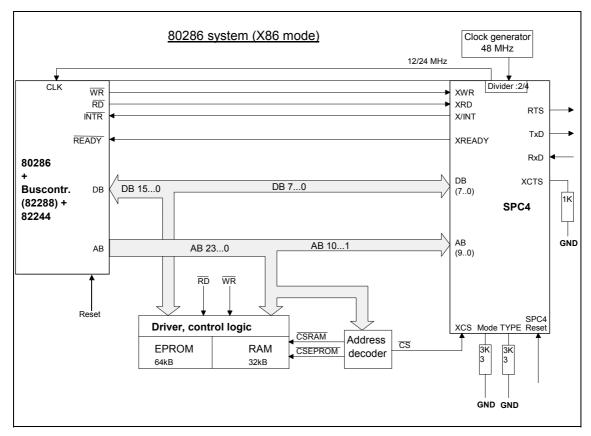

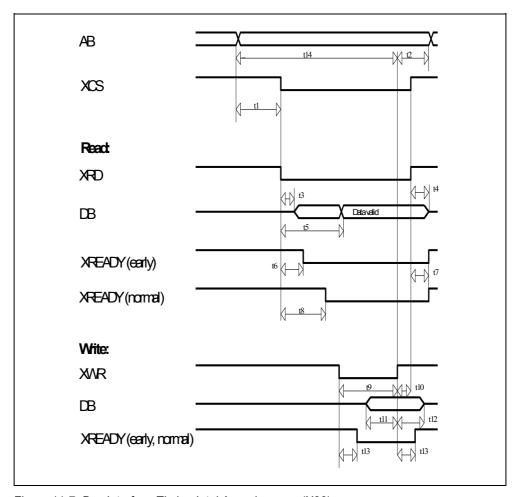

|    | 11.8<br>11.8.1           | Intel X86 (asynchronous)                                                      | 142<br>142 |

|    | 11.9<br>11.9.1<br>11.9.2 | <b>5</b>                                                                      | 145        |

|    | 11.10<br>11.10.          | Timing 68HC16 (asynchronous)                                                  |            |

|    | 11.11<br>11.11.          | Motorola 68HC11 (synchronous)<br>1 Timing 68HC11                              |            |

| 12 | Techn                    | ical Specifications                                                           | 153        |

|    | 12.1                     | Maximum Limit Values                                                          | 154        |

|    | 12.2                     | Permitted Operating Values                                                    | 155        |

|    | 12.3                     | Power Consumption                                                             | 156        |

|    | 12.4                     | DC Specification of the Pad Cells                                             | 157        |

|    | 12.5                     | Ratings of the Output Drivers                                                 | 158        |

| 13 | Packa                    | ge                                                                            | 159        |

|    | 13.1                     | Instructions on Handling                                                      | 161        |

|    | 13.2                     | Labeling                                                                      | 163        |

|    | 13.3                     | Packaging of the ASIC                                                         | 164        |

| 14 | Refer | References10                     |     |  |

|----|-------|----------------------------------|-----|--|

| 15 | Addre | esses                            | 169 |  |

|    | 15.1  | PNO                              | 170 |  |

|    | 15.2  | Contacts in the Interface Center | 171 |  |

| 16 | Appe  | ndix                             | 173 |  |

|    | 16.1  | Server Software for the SPC 4-2  | 174 |  |

|    | 16.2  | SIM1                             | 176 |  |

Introduction

#### **ASICs**

For simple and fast digital exchange between programmable logic controllers, Siemens offers users various ASICs. These ASICs either support or handle the entire data exchange between the automation stations according to the PROFIBUS standards and guidelines DIN 19245 Part 1, Part 2, Part 3 and PROFIBUS PA (Part 4), EN 50170 Volume 2, IEC 61158 Ed.3, and IEC 61784-1. The SPC  $4^{\$}$ -2 also supports the Foundation Fieldbus as described in IEC 61158. Ed3.

#### **Functionality**

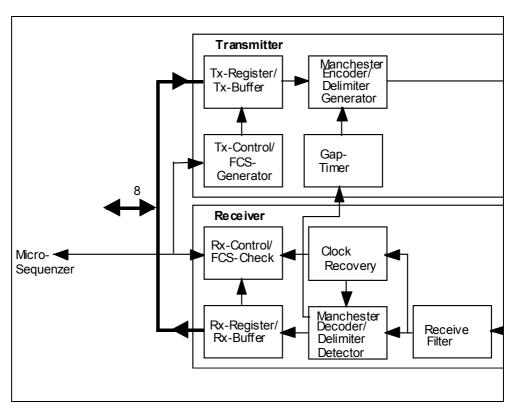

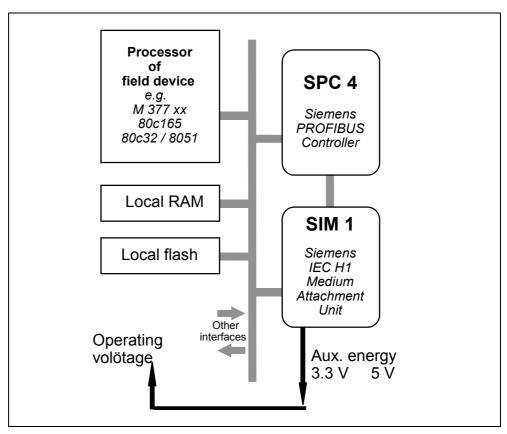

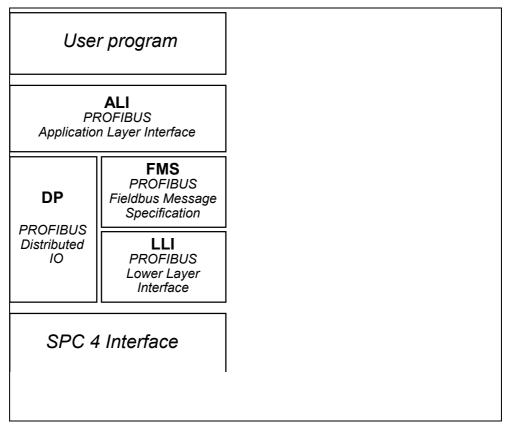

The SPC 4®-2 (Siemens PROFIBUS Controller) operates at layer 1 of the OSI model and requires an additional microprocessor to implement layers 2 and 7.

With the **SPC 4**<sup>®</sup>-2, parts of layer 2 that handle the bus protocol are integrated. For the other functions of layer 2 (interfacing, management) an additional microprocessor is required.

In addition to the layer 2 functionality, the following productive services are also integrated on the ASIC: Data\_Exchange, Read\_Input, Read\_Output and the Global\_Control command of DIN E 19245 Part 3/EN50170/IEC61158 as well as the PROFIBUS-PA functionality (DIN E 19245 Part 4/EN 50170/IEC 61158, IEC 61784-1).

SPC 4-2 supports the following communication profiles:

- PROFIBUS FMS

- PROFIBUS PA

- PROFIBUS DP

- Foundation Fieldbus®<sup>1</sup> (FF).

The communication profiles and the possible combinations with the physical media (copper, glass-fiber) are described in the IEC 61784-1 standard (apart from PROFIBUS-FMS, see EN 50170 Vol. 2).

The SPC 4-2 supports passive nodes on the bus system (slaves) and filters out all external frames and bad data frames.

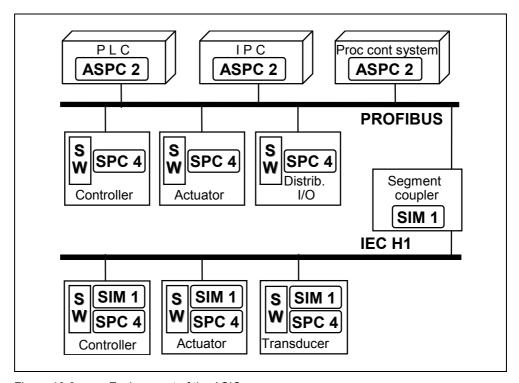

To extend the SPC 4-2 for PROFIBUS PA and FF, the SIM 1 communication interface chip is available. The SIM 1 ASIC implements the function of a Medium Attachment Unit (MAU).

<sup>&</sup>lt;sup>1</sup> Foundation Fieldbus is a registered trademark of Fieldbus Foundation.

Functional Overview 2

Apart from the bus drivers, the SPC 4-2 contains the entire PROFIBUS peripherals. The additional processor does not need to provide a hardware timer to process the bus protocol.

Baud rates from 9.6 kbit/s to 12 Mbit/s are supported. The SIM 1 ASIC is an ideal extension for PROFIBUS PA.

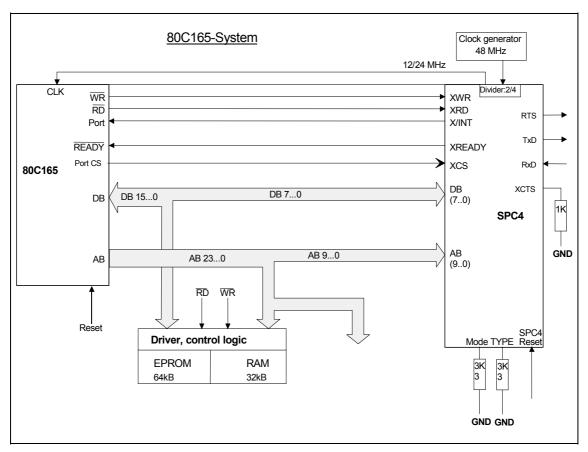

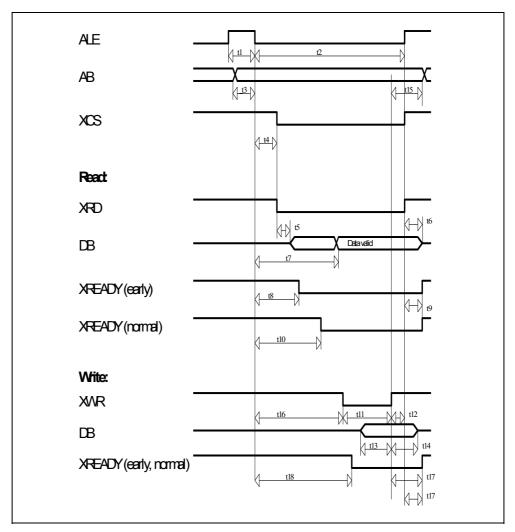

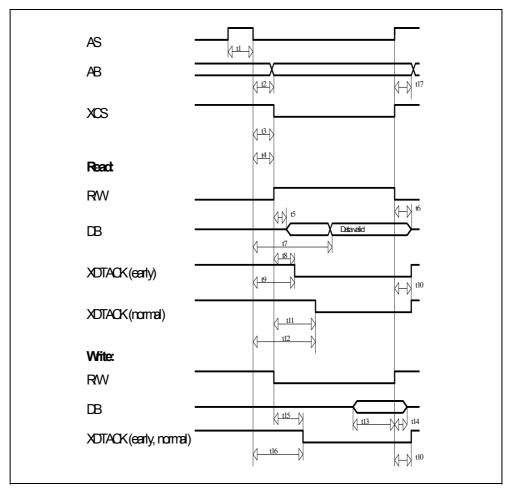

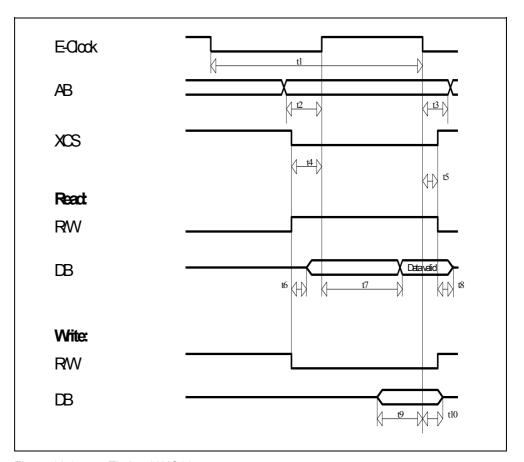

The SPC 4-2 has a universal microcontroller interface with an 8-bit data bus interface and a 10-bit address bus. Depending on the configuration, the data/address but can be operated separately or multiplexed so that processors with the standard x86 timing, the Motorola timing, the SAB C165 timing, or an 80C32 timing can be connected.

Since the interface supports both INTEL and MOTOROLA architectures, the Intel or Motorola data format is selected with two configuration pins along with the synchronous (rigid timing) or asynchronous (with Ready support) processor bus timing.

The handshake between the processor and the SPC 4-2 is executed by the FLC firmware (Field Bus Link Control; synonym for all communication stacks) via the dual-port RAM (extended to 3 Kbytes) integrated on the SPC 4-2.

From the point of view of the user, the SPC 4-2 occupies an address space of 1 Kbyte.

The plausibility check when request frames are received is handled by the SPC 4-2.

#### **Pulse Modulation**

The SPC 4-2 has circuits for a direct connection SIM 1-optocoupler-SPC 4-2 (PROFIBUS PA attachment) using the current-saving interface of the SIM. A separate adapter circuit is no longer necessary.

The frames received from the SIM 1 are converted to a series of short pulses and then passed on to the SPC 4-2.

#### **Fast Synchronizer in the Manchester Receiver**

Fast synchronization means finding the bit mid point in the preamble of a Manchester frame (PROFIBUS PA). This allows the SPC 4-2 to tolerate larger systematic distortion (all rising or falling edges are delayed by the same amount).

## Compatibility with SPC 4/4-1

The SPC 4<sup>®</sup>-2 is compatible with the ASIC SPC 4<sup>®</sup> and SPC 4<sup>®</sup>1. This compatibility includes the mechanical and electrical properties as well as the functions used via a software interface.

## Additional properties of the SPC 4-2

- Optional use of PROFIBUS and Foundation Fieldbus by changing the firmware

- *PROFI*Safe prepared (slave-slave communication)

- PROFIDrive support (clock pulse output)

- Time-of-day synchronization for time stamping alarms and events

- Memory expanded from 2K to 3K

- Diagnostic output

- Selectable unsharpness window of the pulse modulation

The expansions of the SPC 4-2 are activated using previously unused parameter registers. The SPC 4/SPC 4-1 does not evaluate address bits 7 to 5 when the parameter registers are accessed so that all registers can be accessed under several addresses (write and read). All the SPC 4/SPC 4-1 and 4 new SPC 4-2 registers are within this accessible address space. By activating the "Enable SPC 4-2" bit, the SPC 4-2 evaluates all address bits.

The SPC 4-2 contains 4 new 16-bit timers. These can be used in the FF mode since they use interrupt bits that are only free in the FF mode. All the timers are clocked at the baud rate and can be operated as "One-Shot" or as "Cyclic" timers.

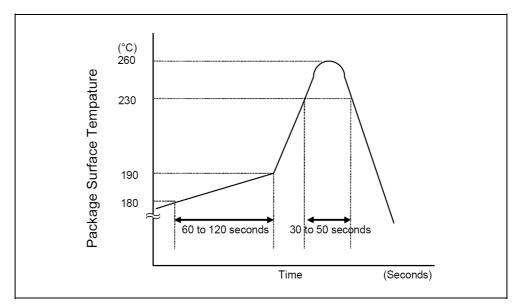

### Additional properties of the SPC 4-2 LF

- Meets the requirements of the EU directive:

2002L0095 EN 01.07.2006 002.001 1

- Can be used with lead-free and lead solder techniques

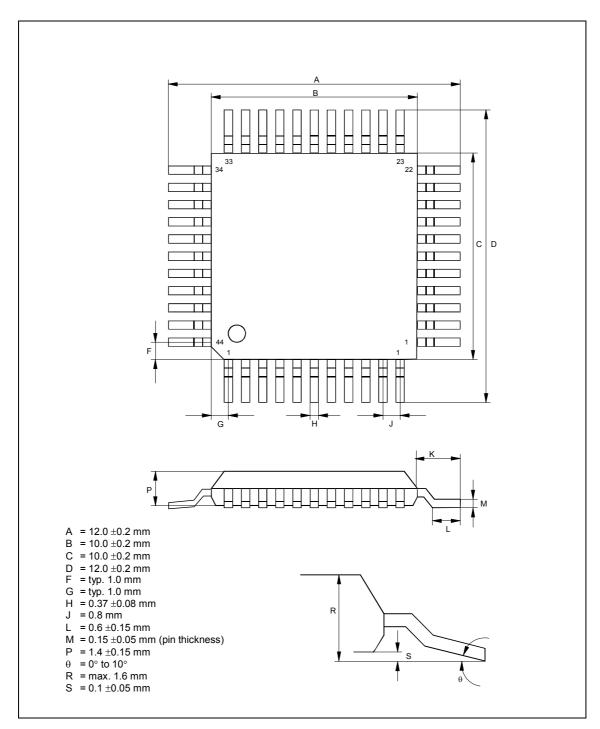

- New package type 44-pin LQFP

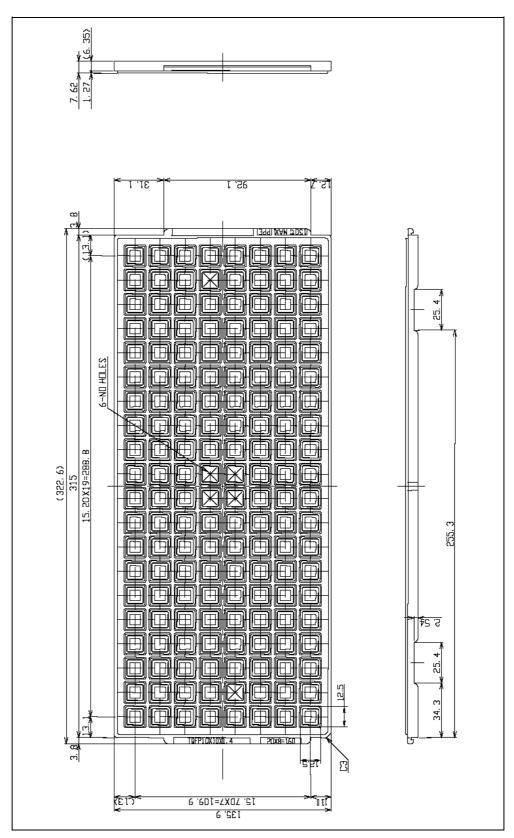

- New delivery packaging

**Pin Assignment**

3

The SPC 4-2 has a 44-pin *plastic quad flat package* housing (see Chapter 11). The pin assignment is described in Table 3-1 Pin Assignment

**Note:** All signals that start with X.. are LOW-active

| Pin Signal name |                  | ln/ | Description                                                                                            | Source / Dest         | Processor                                              |

|-----------------|------------------|-----|--------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------|

|                 |                  | Out |                                                                                                        |                       | Variant                                                |

| 1               | XCS              | I   | Chip select                                                                                            | CPU                   | C32 mode: connect<br>to VDD<br>otherwise: CS<br>signal |

| 2               | XWR / E          | I   | Write signal E-clock with Motorola 1 clock pulse=1 memory cycle (in asynchronous mode, connect to VDD) | CPU                   |                                                        |

| 3               | DIVIDER          | 1   | Divider for ISCLK-OUT (pin 7)<br>0=:4, 1=:2                                                            | System                |                                                        |

| 4               | XRD<br>R/W       | I   | Read signal<br>Read/Write with Motorola<br>(low=write)                                                 | CPU                   |                                                        |

| 5               | CLK              | 1   | Clock input                                                                                            | System                |                                                        |

| 6               | VSS              |     |                                                                                                        |                       |                                                        |

| 7               | ISCLK-Out        | L   | Input clock, divided by 2 or 4                                                                         | System, CPU           |                                                        |

| 8               | Туре             | I   | Data format of processor interface (see Mode Table)                                                    |                       |                                                        |

| 9               | XINT             | L   | Interrupt output                                                                                       | CPU, Interrupt-Contr. |                                                        |

| 10              | XINTCI           | L   | Port pin in the compatibility mode, in the extended mode interrupt output clock synchronization        | CPU, Interrupt-Contr. | Port pin bit 1 of mode register 2                      |

| 11              | DB0              | I/O | Data bus                                                                                               | CPU, memory           | C32 mode:<br>data/address bus<br>multiplexed           |

| 12              | DB1              | I/O | Data bus                                                                                               | CPU, memory           | Otherwise:<br>data/address bus<br>separate             |

| 13              | XHOLDTOKEN       | L   | Port pin in compatibility mode, in extended mode trigger output for measurements                       |                       | Port pin bit 0 of mode register 2                      |

| 14              | XREADY<br>XDTACK | L   | Ready for external CPU Data transfer acknowledge with Motorola  System, CPU System, CPU                |                       |                                                        |

| 15              | DB2              | I/O | Data bus CPU, memory                                                                                   |                       | C32 mode:<br>data/address bus<br>multiplexed           |

| 16              | DB3              | I/O | Data bus CPU, memory                                                                                   |                       | Otherwise:<br>data/address bus<br>separate             |

| 17              | VSS              |     |                                                                                                        |                       |                                                        |

| 18              | VDD              |     |                                                                                                        |                       |                                                        |

| 19              | DB4              | I/O | Data bus                                                                                               | CPU, memory           | C32 mode: data                                         |

| Pin | Signal name | In/<br>Out | Description                                                            | Source / Dest      | Processor<br>Variant               |

|-----|-------------|------------|------------------------------------------------------------------------|--------------------|------------------------------------|

| 20  | DB5         | I/O        | Data bus                                                               | CPU, memory        | /address bus<br>multiplexed        |

| 21  | DB6         | I/O        | Data bus                                                               | CPU, memory        | Otherwise:<br>data/address bus     |

| 22  | DB7         | I/O        | Data bus                                                               | CPU, memory        | separate                           |

| 23  | MODE        | I          | Timing format of the processor interface (see Mode Table)              | System             |                                    |

| 24  | ALE         | I          | Address latch enable                                                   | CPU                | C32 mode: ALE                      |

|     | AS          |            | Address strobe with Motorola (in synchronous operation connect to VDD) |                    | Motorola mode<br>AS                |

| 25  | AB9         | I          | Address bus                                                            | CPU                | C32 mode: : <log> 0</log>          |

| 26  | TXD-TXS     | L          | Serial transmit channel                                                | RS-485 transmitter |                                    |

| 27  | RTS-ADD     | L          | Request To Send                                                        | RS-485 transmitter |                                    |

| 28  | vss         |            |                                                                        |                    |                                    |

| 29  | AB8         | I          | Address bus                                                            | System, CPU        | C32 mode: <log></log>              |

| 30  | RXD-RXS     | I          | Serial receive channel                                                 | RS-485 receiver    |                                    |

| 31  | AB7         | I          | Address bus                                                            | System, CPU        | C32 mode: <log></log>              |

| 32  | AB6         | I          | Address bus System, CPU                                                |                    | C32 mode: <log><br/>0 for CS</log> |

| 33  | XCTS        | I          | Clear to Send <log> 0 = clear to MODEM/FSK send</log>                  |                    |                                    |

| 34  | XTEST0      | I          | Pin must be connected to VDD.                                          |                    |                                    |

| 35  | XTEST1      | I          | Pin must be connected to VDD.                                          |                    |                                    |

| 36  | RESET       | I          | Reset input: connect to port pin of CPU                                |                    |                                    |

| 37  | AB4         | I          | Address bus                                                            | System, CPU        | C32 mode: <log><br/>0 for CS</log> |

| 38  | vss         |            |                                                                        |                    |                                    |

| 39  | VDD         |            |                                                                        |                    |                                    |

| 40  | AB3         | I          | Address bus System, CPU                                                |                    | C32 mode: <log><br/>0 for CS</log> |

| 41  | AB2         | I          | Address bus System, CPU                                                |                    | C32 mode: <log><br/>0 for CS</log> |

| 42  | AB5         | I          | Address bus System, CPU                                                |                    | C32 mode: <log><br/>0 for CS</log> |

| 43  | AB1         | I          | Address bus System, CPU                                                |                    | C32 mode:<br>address window        |

| 44  | AB0         | I          | Address bus                                                            | System, CPU        | C32 mode:<br>address window        |

Table 3-1 Pin Assignment

**Memory Assignment**

4

## 4.1 Addressing the SPC 4-2

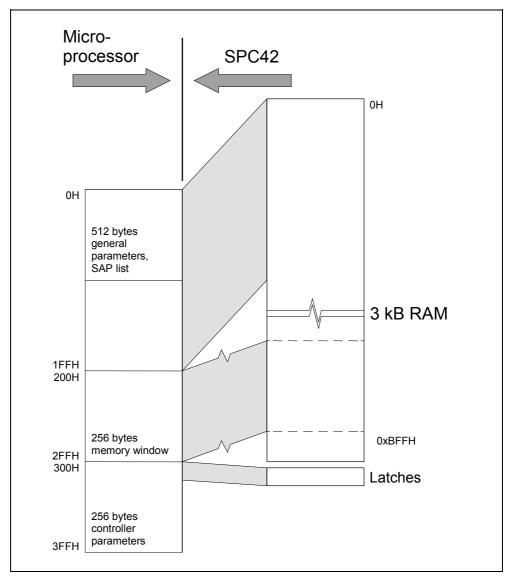

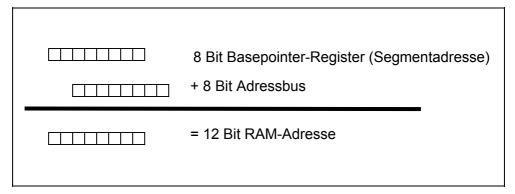

From the user perspective, the 3-Kbyte internal dual-port RAM and the internal latches occupy a 1-Kbyte address space. Parts of the internal RAM are located directly in the address range of the microprocessor, the other parts can be addressed using a window mechanism, see Figure 4-1

Figure 4-1 Addressing the Internal 3-Kbyte RAM

#### **Address Window**

With the lower address window, the FLC can access the first 512 (2 x 256) bytes of the RAM physically without needing to load the base pointer. The advantage of this is that the FLC can access the general parameters or the SAP list directly without first needing to load the base pointer.

The entire internal memory can be addressed via the second address window of 256 bytes (200h to 2FFh) with the aid of an 8-bit base pointer. This pointer must be loaded by the FLC and always addresses the beginning of an 8 byte segment (in the extended SPC 4-2 mode, 16 bytes). This means that the FLC can address up to 256 bytes using the offset address applied to the address pins of the SPC 4-2.

The third address window which is also 256 bytes long (300h to 3FFh) is used to address the internal latches required for direct control of the hardware. These latches are not integrated in the internal RAM area!

| Address bit<br>A9 | Address bit<br>A8 | Window Select                         |  |

|-------------------|-------------------|---------------------------------------|--|

| 0                 | 0                 | Parameter area (physically 00h-FFh)   |  |

| 0                 | 1                 | Parameter area (physically 100h-1FFh) |  |

| 1                 | 0                 | Entire RAM using base pointer         |  |

| 1                 | 1                 | Parameter register                    |  |

Table 4-2 Window Select

#### Notice:

Overwriting the address area is not prevented by the hardware; in other words, if the user writes beyond the node table, the parameters are overwritten in the lower memory area due to the "wraparound" function. In this case, the SPC 4-2 generates the Mem-Overflow interrupt. If read-only parameters are written to, an access violation interrupt is generated.

## 4.2 Structure of the Internal RAM

#### 4.2.1 Overview

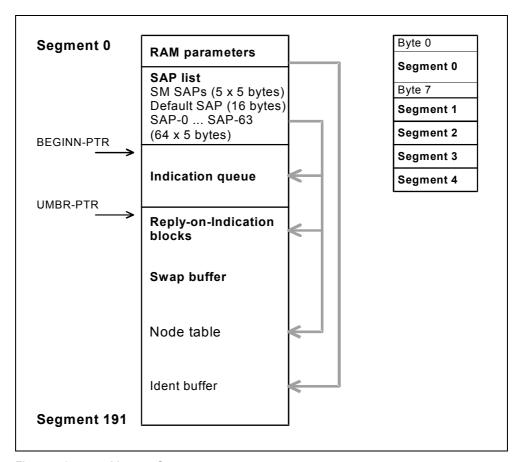

Figure Figure 4-3 shows the structure of the internal 3 Kbyte RAM of the SPC 4-2. The entire memory area made up of segments of 8 bytes (or 16 bytes in the extended SPC 4-2 mode) is divided into different areas.

Figure 4-3 Memory Structure

### 4.2.2 RAM Parameter Block

The first 6 or 8 bytes of the integrated RAM contain the general parameters such as the read and write pointers of the indication queue that do not intervene directly in the controller, see Table 4-4. The FLC is permitted to write only the parameters with addresses 00H to 5H or 7H. The internal working cells must not be overwritten (the hardware generates a write-violation interrupt and goes offline).

| Address | Name                   | Access  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Meaning                                                                                                                                                                                      |  |

|---------|------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 00H     | IND-WP-<br>PRE         | RD/WR   | The write pointer for indication preprocessing points to the next free segment that follows the last request frame received even when no indication "IND" has been received. The IND-WP-PRE pointer allows a fast slave reaction (for example for PROFIBUS DP). The IND-WP-PRE pointer is set to the next free segment boundary immediately after receiving a request frame correctly (even before a response frame is sent). At the same time, the "IND-PRE" interrupt is generated. |                                                                                                                                                                                              |  |

| 0411    | INID W/D               | DD AA/D | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ust not be changed by the FLC.                                                                                                                                                               |  |

| 01H     | IND-WP                 | RD/WR   | free segment f<br>With each "IND                                                                                                                                                                                                                                                                                                                                                                                                                                                      | of the indication queue pointing to the next collowing the last indicated request frame.  "Indication interrupt, IND-WP is set to a poundary by the SPC 4-2. This pointer must d by the FLC. |  |

| 02H     | IND-RD                 | RD/WR   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | er of the indication queue is also a segment managed by the FLC.                                                                                                                             |  |

| 03H     | FDL-Ident-<br>Ptr      | RD/WR   | Pointer to the I                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | dent buffer                                                                                                                                                                                  |  |

| 04H     | TS-ADR-<br>REG         | RD/WR   | Contains the node address                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                              |  |

|         |                        |         | PROFIBUS PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |  |

|         |                        |         | 0 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Normal node                                                                                                                                                                                  |  |

|         |                        |         | 120124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Temporary node (for example handheld)                                                                                                                                                        |  |

|         |                        |         | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Default address for temporary nodes                                                                                                                                                          |  |

|         |                        |         | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Default address for permanent nodes                                                                                                                                                          |  |

|         |                        |         | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Broadcast/multicast                                                                                                                                                                          |  |

|         |                        |         | PROFIBUS I                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DP                                                                                                                                                                                           |  |

|         |                        |         | 0 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Normal node (recommended for slave: 3125)                                                                                                                                                    |  |

|         |                        |         | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Default address for address assignment                                                                                                                                                       |  |

|         |                        |         | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Broadcast/multicast                                                                                                                                                                          |  |

| 05H     | SAP-MAX                | RD/WR   | The highest SA                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AP list number is set                                                                                                                                                                        |  |

| 06H     | AQUI-ADR               | RD/WR   | Station address of the valid constant bus cycle time master (exists only in SPC 4-2 mode, otherwise a write violation interrupt is generated in response to write access)                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                              |  |

| 07H     | GRP-BYTE               | RD/WR   | Group selection byte for clock synchronization (exists only in SPC 4-2 mode, otherwise a write violation interrupt is generated in response to write access)                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                              |  |

| 08H17H  | Internal<br>work cells |         | The following of interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                           | cells must not be overwritten (write-violation                                                                                                                                               |  |

Table 4-4 Assignment of the RAM Parameter Block

Access to the parameter registers or the internal RAM require not only the correct connection of the relevant address bits but also the connection of an XCS signal to the SPC 4-2. In addition to this, the XREADY signal of the SPC 4-2 must be taken into account or suitable wait states must be created.

#### Note

When writing the RAM parameters, the upper unused bits must be set to '0' while the unused bit positions in the parameter registers are 'don't care'.

#### 4.2.3 SAP List

The SAP list can be addressed directly and no segmentation or use of the base pointer is required although it is also possible to use the base pointer for addressing. To access the data to which a SAP points, the base pointer must be used.

The area of the service access points (SAPs) occupies 361 bytes (address 18H .. 180H). The SAP list is made up of the following:

- 5 SM-SAPs (System Management Service Access Point) each 5 bytes long

- DEFAULT-SAP (Service Access Point) with 16 bytes

- 64 SAPs each 5 bytes long

Table 5-1 shows the SAP list, the functions of the individual registers and bits are explained in the following sections.

### 4.2.4 Data Areas in the Internal RAM

#### **Indication Queue**

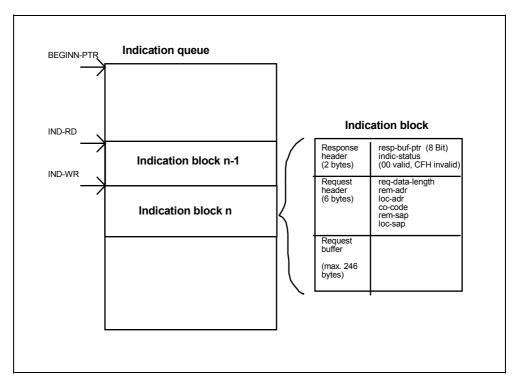

Following the SAP list, there is a memory area for the indication queue. The address area can be set at segment boundaries by the FLC. The first possible address in the compatibility mode (8 byte segment size) is 188H, in the extended SPC 4-2 mode it is 190H.

The BEGIN-PTR is the address of the first segment of the indication queue. The end of the queue is indicated by UMBR-PTR. The UMBR-PTR points to the address of the first segment that **no longer** belongs to the indication queue.

#### Caution

After initialization in the offline mode, both pointers must be set to the required start of the range. THEY CANNOT BE MODIFIED DYNAMICALLY; in other words, to modify the memory assignment, the SPC 4-2 must be changed to offline. A change in the order of the pointers leads to an incorrect response of the SPC 4-2 related to the individual memory areas.

If the SPC 4-2 receives request frames, it enters them in the indication queue. The indication queue is organized as a ring buffer; in other words the data to be processed is entered one after the other in the queue as long as there is still space in the queue and blocks that have been processed are taken out of the queue. The indication queue is organized using write and read pointers. The indication read pointer (IND-RP) must be set by the FLC while the hardware of the SPC 4-2 is responsible for updating the indication write pointer (IND-WP).

Since this is a ring buffer, the end of the queue must be monitored when data are entered. If this is exceeded, the address must be wrapped. The SPC 4-2 provides hardware support that automatically wraps the address.

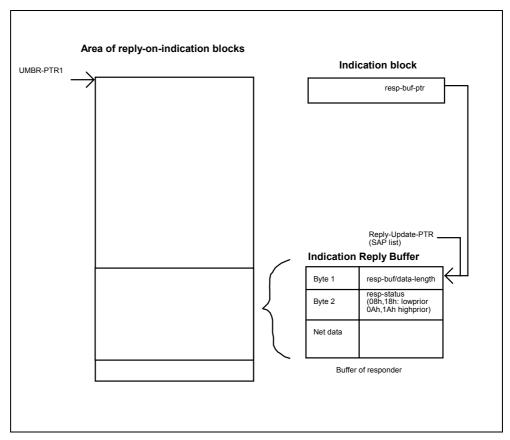

#### **Reply-on-Indication Blocks**

The FLC must provide reply data in these buffers. The reply data are assigned to the calls using pointers in the SAP lists.

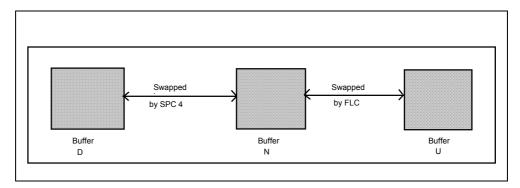

## **Swap Buffers**

To support PROFIBUS DP services (DP mode = 1 in the mode register 0), 6 swap buffers must be provided.

#### **Ident Buffer**

The Ident buffer contains the reply data for Ident frames.

#### **Node Table**

The node table is required to filter SDN or DDB response frames.

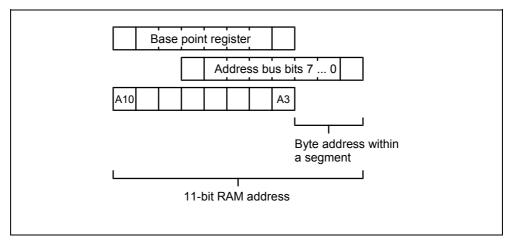

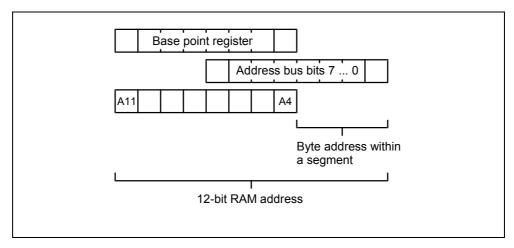

## 4.2.5 Addressing Using the Memory Window

When addressing the SPC 4-2, the physical address of the integrated RAM is formed via the second address window (200h to 2FFh) from the base pointer, the segment address for the indication queue and the lower 8 bits of the address bus. The base pointer is added to the address of the address that is shifted by three or four bit positions, see Figure 4-5.

In the extended SPC 4-2 mode, the base pointer is shifted by 4 bits instead of by 3 bits to the left so that the segment size is then 16 bytes instead of 8 bytes.

New segment address = base pointer + AB7..3 - end pointer + begin pointer

8-byte segment in the compatibility mode

New segment address = base pointer + AB7..4 - end pointer + begin pointer

16-byte segment in the SPC 4-2 mode

Along with the 3 or 4 least significant address bits, the result forms the physical 11-bit or 12-bit address for the internal RAM. With the calculator, the FLC can address up to 256 data bytes once the base pointer is loaded without having to reload the base pointer or worry about the wrapping at the queue limit.

Figure 4-5 Calculating the Physical RAM Address in the Compatibility Mode

Figure 4-6 Calculating Physical RAM Address in the Extended SPC 4-2 Mode

## 4.3 Assignment of the Parameter Registers

It is only possible to access the internal parameter registers (in other words, the memory cells that intervene directly in the controller) using the address window 300h to 3FFh on the SPC 4-2.

These cells can either only be read or only be written and have different functions. In the Motorola mode, the SPC 4-2 swaps addresses for access to the address range starting at 300H (word register); in other words, it swaps the address bit 0 (generates an odd address from an even address and vice versa).

The SPC 4-2 has an 8-bit data interface. When the byte registers are accessed via this interface, it does not matter whether the SPC 4-2 is in the Intel or in the Motorola mode.

When the word registers are accessed (two-byte registers), the SPC 4-2 distinguishes between the Intel and Motorola mode.

Example: INT-MASK-REG

Intel mode: Write access with address 300

⇒ INT-MASK-REG (7..0) is written (little endian)

Motorola mode: Write access with address 300

⇒ INT-MASK-REG (15..8) is written (big endian)

This means that the high byte and low byte are addressed with different addresses.

The meaning of the individual bits in the registers is explained in greater detail in the following sections.

Since the addresses of the parameter registers are not fully coded, the registers appear again every 64 bytes. This simplifies the implementation since different addresses (names) can be assigned for read and write access.

| Address<br>Intel /Motorola |                  | Name             | Meaning (READ access !)                                                          |

|----------------------------|------------------|------------------|----------------------------------------------------------------------------------|

| 300 <sub>H</sub>           | 301 <sub>H</sub> | Int-Req-Reg 70   | Interrupt controller register                                                    |

| 301н                       | 300 <sub>H</sub> | Int-Req-Reg 158  |                                                                                  |

| 302 <sub>H</sub>           | 303 <sub>H</sub> | Int-Reg 70       |                                                                                  |

| 303 <sub>H</sub>           | 302 <sub>H</sub> | Int-Reg 158      |                                                                                  |

| 304 <sub>H</sub>           | 305 <sub>H</sub> | Status-Reg 70    | Status Register                                                                  |

| 305 <sub>H</sub>           | 304 <sub>H</sub> | Status-Reg 158   |                                                                                  |

| 306н                       | 307н             | Delay 70         | Delay timer register, current counter reading                                    |

| 307 <sub>H</sub>           | 306 <sub>H</sub> | Delay 158        |                                                                                  |

| 308 <sub>H</sub>           | 309 <sub>H</sub> | reserved         |                                                                                  |

| 309 <sub>H</sub>           | 308 <sub>H</sub> | reserved         |                                                                                  |

| 30A <sub>H</sub>           | 30B <sub>H</sub> | reserved         |                                                                                  |

| 30B <sub>H</sub>           | 30A <sub>H</sub> | reserved         |                                                                                  |

| 30C <sub>H</sub> - 30      | )F <sub>H</sub>  | reserved         |                                                                                  |

| 310 <sub>H</sub>           |                  | Delay 2316       | Extension of the delay timer register                                            |

| 311 <sub>H</sub>           |                  | reserved         |                                                                                  |

| 312 <sub>H</sub>           |                  | reserved         |                                                                                  |

| 313 <sub>H</sub>           |                  | reserved         |                                                                                  |

| 314 <sub>H</sub>           |                  | reserved         |                                                                                  |

| 315 <sub>H</sub>           |                  | reserved         |                                                                                  |

| 316 <sub>H</sub>           |                  | reserved         |                                                                                  |

| 317 <sub>H</sub>           |                  | reserved         |                                                                                  |

| 318 <sub>H</sub>           |                  | Mem-Lock 0       | Memory lock cell                                                                 |

| 319 <sub>H</sub>           |                  | reserved         |                                                                                  |

| 31A <sub>H</sub>           |                  | reserved         |                                                                                  |

| 31B <sub>H</sub>           |                  | reserved         |                                                                                  |

| 31C <sub>H</sub>           |                  | reserved         |                                                                                  |

| 31D <sub>H</sub>           |                  | reserved         |                                                                                  |

| 31E <sub>H</sub>           |                  | reserved         |                                                                                  |

| 31F <sub>H</sub>           |                  | reserved         |                                                                                  |

| 320 <sub>H</sub>           |                  | Timer0-Reg 158   | Timer 0 high byte 158 (only SPC 4-2 mode)                                        |

| 321 <sub>H</sub>           |                  | Timer0-Reg 70    | Timer 0 low byte 70 (only SPC 4-2 mode)                                          |

| 322 <sub>H</sub>           |                  | Timer1-Reg 158   | Timer 1 high byte 158 (only SPC 4-2 mode)                                        |

| 323 <sub>H</sub>           |                  | Timer1-Reg 70    | Timer 1 low byte 70 (only SPC 4-2 mode)                                          |

| 324 <sub>H</sub>           |                  | Timer2-Reg 158   | Timer 2 high byte 158 (only SPC 4-2 mode)                                        |

| 325 <sub>H</sub>           |                  | Timer2-Reg 70    | Timer 2 low byte 70 (only SPC 4-2 mode)                                          |

| 326 <sub>H</sub>           |                  | Timer3-Reg 158   | Timer 3 high byte 158 (only SPC 4-2 mode)                                        |

| 327 <sub>H</sub>           |                  | Timer3-Reg 70    | Timer 3 low byte 70 (only SPC 4-2 mode)                                          |

| 328 <sub>H</sub>           |                  | Error-Hi-Reg 158 | Error counter register high byte 158 (only SPC4-2 mode) for error trigger signal |

| 329 <sub>H</sub>           |                  | Error-Lo-Reg 70  | Error register low byte 70 (SPC4-2 mode only)                                    |

Table 4-7 Assignment of the Internal Parameter Registers (Only for Read Access)

| Address<br>Intel/Motorola |                  | Name                                  | Meaning (write access !)                                                                                                                           |

|---------------------------|------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 300 <sub>H</sub>          | 301 <sub>H</sub> | Int-Mask-Reg 70                       | Interrupt controller register                                                                                                                      |

| 301 <sub>H</sub>          | 300 <sub>H</sub> | Int-Mask-Reg 158                      |                                                                                                                                                    |

| 302 <sub>H</sub>          | 303 <sub>H</sub> | Int-Ack-Reg 70                        |                                                                                                                                                    |

| 303 <sub>H</sub>          | 302 <sub>H</sub> | Int-Ack-Reg 158                       |                                                                                                                                                    |

| 304 <sub>H</sub>          | 305 <sub>H</sub> | TSLOT 70                              | Settings for the wait-to-receive time                                                                                                              |

| 305н                      | 304н             | TSLOT 138                             |                                                                                                                                                    |

| 306 <sub>H</sub>          | 307 <sub>H</sub> | BR-REG 70                             | Setting of the dividing factor                                                                                                                     |

| 307 <sub>H</sub>          | 306 <sub>H</sub> | BR-REG 108                            | For generating the baud rate                                                                                                                       |

| 308 <sub>H</sub>          | 309 <sub>H</sub> | TID1 70                               |                                                                                                                                                    |

| 309 <sub>H</sub>          | 308 <sub>H</sub> | TID1 108                              |                                                                                                                                                    |

| 30A <sub>H</sub>          | 30B <sub>H</sub> | FAKT-DEL-CLK 70                       | Delay timer for SM time service                                                                                                                    |

| 30B <sub>H</sub>          | 30A <sub>H</sub> | FAKT-DEL-CLK 108                      |                                                                                                                                                    |

| 30C <sub>H</sub> - 30     | )F <sub>H</sub>  | reserved                              |                                                                                                                                                    |

| 310 <sub>H</sub>          |                  | UMBR-PTR 70                           | UMBR-PTR points to the address of the first segment that <b>no longer</b> belongs to the indication queue.                                         |

| 311 <sub>H</sub>          |                  | Mode-Reg 70                           | Settings for individual bits                                                                                                                       |

| 312 <sub>H</sub>          |                  | Mode-Reg1-Res 50                      |                                                                                                                                                    |

| 313 <sub>H</sub>          |                  | Mode-Reg1-Set 50                      |                                                                                                                                                    |

| 314 <sub>H</sub>          | Base-PTR 70      |                                       | Base address for access to the internal RAM                                                                                                        |

| 315 <sub>H</sub>          |                  | TRDY 70                               | Settings for TRDY (ready time valid before sending a reply frame)                                                                                  |

| 316н                      |                  | PREAMBLE                              | Settings for the number of bits (preamble) in the synchronous mode.                                                                                |

| 317 <sub>H</sub>          |                  | TSYN                                  | The following time is set:                                                                                                                         |

|                           |                  |                                       | TSYN (33-bit asynchronous mode)                                                                                                                    |

|                           |                  |                                       | TIFG (interframe GAP time; synchronous mode)                                                                                                       |

| 318 <sub>H</sub>          |                  | Mem-Lock 0                            | Memory lock cell                                                                                                                                   |

| 319 <sub>н</sub>          |                  | BEGIN-PTR 70                          | The BEGIN-PTR points to the lowest segment address of the indication queue. The BEGIN-PTR must always point to the beginning of an 8-byte segment. |

| 31A <sub>H</sub>          |                  | Mode-Reg2 70                          | Settings for individual bits                                                                                                                       |

| 31B <sub>H</sub>          |                  | Mode-Reg3 70                          | Settings for individual bits                                                                                                                       |

| 31C <sub>H</sub>          |                  | Mode-Reg4 70                          | Settings for individual bits (only SPC 4-2 mode)                                                                                                   |

| 31D <sub>H</sub>          |                  | Timer-Typ-Reg 70                      | Mode setting time 03 (only SPC 4-2 mode)                                                                                                           |

| 31E <sub>H</sub>          |                  | Timer-Control-Reg 70                  | Status control timer 03 (only SPC 4-2 mode)                                                                                                        |

| 31F <sub>H</sub>          |                  | Clocked counter end value register 30 | End value for counters of clocked frames (only SPC 4-2 mode)                                                                                       |

| 320 <sub>H</sub>          |                  | Timer0-Reg 158                        | Timer 0 high byte 158 (only SPC 4-2 mode)                                                                                                          |

| 321 <sub>H</sub>          |                  | Timer0-Reg 70                         | Timer 0 low byte 70 (only SPC 4-2 mode)                                                                                                            |

| 322 <sub>H</sub>          |                  | Timer1-Reg 158                        | Timer 1 high byte 158 (only SPC 4-2 mode)                                                                                                          |

| 323 <sub>H</sub>          |                  | Timer1-Reg 70                         | Timer 1 low byte 70 (only SPC 4-2 mode)                                                                                                            |

| 324 <sub>H</sub>          |                  | Timer2-Reg 158                        | Timer 2 high byte 158 (only SPC 4-2 mode)                                                                                                          |

| 325 <sub>H</sub>          |                  | Timer2-Reg 70                         | Timer 2 low byte 70 (only SPC 4-2 mode)                                                                                                            |

| 326н                      |                  | Timer3-Reg 158                        | Timer 3 high byte 158 (only SPC 4-2 mode)                                                                                                          |

| 327 <sub>H</sub>          |                  | Timer3-Reg 70                         | Timer 3 low byte 70 (only SPC 4-2 mode)                                                                                                            |

| Address<br>Intel/Motorola | Name             | Meaning (write access !)                                                |

|---------------------------|------------------|-------------------------------------------------------------------------|

| 328 <sub>H</sub>          | Error-Hi-Reg 158 | Writing to this register also deletes Error-Hi-Reg and Error-<br>Lo-Reg |

| 329 <sub>H</sub>          | Error-Lo-Reg 70  | Writing to this register also deletes Error-Hi-Reg and Error-<br>Lo-Reg |

Table 4-8 Assignment of the Internal Parameter Registers (Only for Write Access)

FLC Interface

## 5.1 SAP List

## 5.1.1 Structure of the SAP List

The SAP list is made up as follows:

- 5 SM-SAPs (System Management Service Access Point) each 5 bytes long

- DEFAULT-SAP (Service Access Point) with 16 bytes

64 SAPs each 5 bytes long

| Address       | Name                | register                                  | Meaning                             |

|---------------|---------------------|-------------------------------------------|-------------------------------------|

| 18H           | SM1                 | Control Byte                              | Bit information                     |

| 19H           | 1                   | Request-SA                                | Request source address              |

| 1AH           |                     | reserved                                  |                                     |

| 1BH           | 1                   | reserved                                  |                                     |

| 1CH           | 1                   | Reply-Update-Ptr/                         | Pointer to the reply buffer         |

|               |                     | SDN-DDB/-Tln-Tab-Ptr                      |                                     |

| 1DH - 21H     | SM2                 | analogous to SM1                          | analogous to SM1                    |

| 22H - 26H     | SM3                 | analogous to SM1                          | analogous to SM1                    |

| 27H - 2BH     | SM4                 | analogous to SM1                          | analogous to SM1                    |

| 2CH - 30H     | SM5                 | analogous to SM1                          | analogous to SM1                    |

| 31H           | DEFAULT<br>SAP      | Control byte                              | Bit information                     |

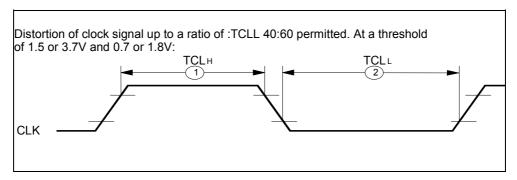

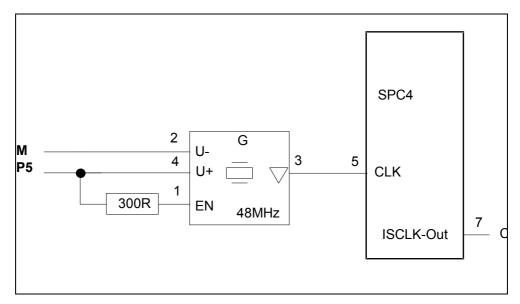

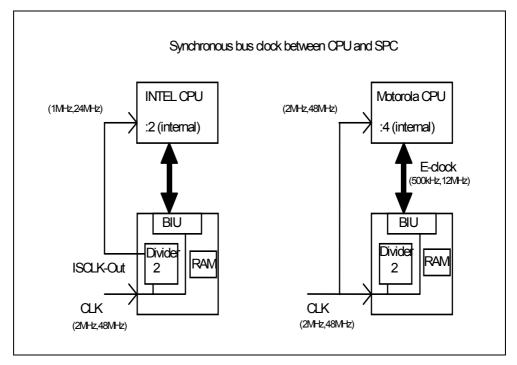

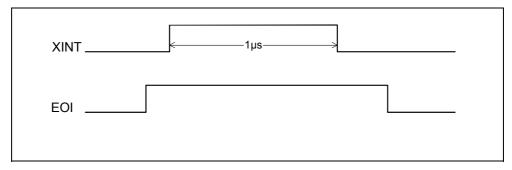

| 32H           |                     | Request-SA                                | Request source address              |